-

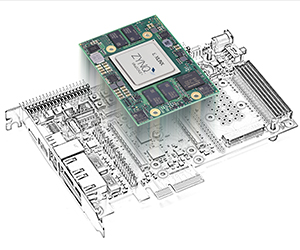

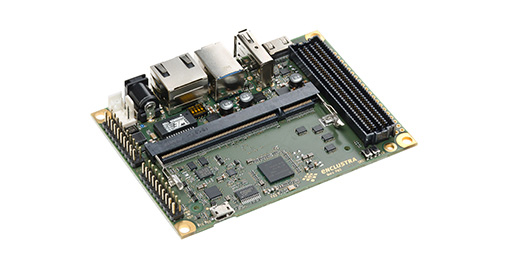

核心板模块

Xilinx Zynq RFSoC

仙女座XRU50核心板(早期试用阶段)

集成 8 路 RF-ADC,采样率高达 5 GSPS;8 路 RF-DAC,采样率高达 9.85 GSPS

基于 AMD Zynq™ UltraScale+™ RFSoC FPGA 架构

四核 Cortex-A53 处理器,主频 1.5 GHz

支持 工业级温度范围

PS:8GB DDR4 SDRAM(ECC),PL:8GB DDR4 SDRAM

配备 5 组 Samtec ADM6-60 连接器,提供多达 202 个用户 I/O

支持 PCIe Gen3 x16、PCIe Gen2 x4、2 路千兆以太网及 USB 3.0 接口

Gbps高速收发器(MGT):16 路 PL GTY:速率高达 28.21 Gbps;4 路 PS GTR:速率高达 6 Gbps

Linux 板级支持包(BSP)及工具链即将推出

高性能紧凑型 FPGA 板卡

Xilinx Zynq MPSoC

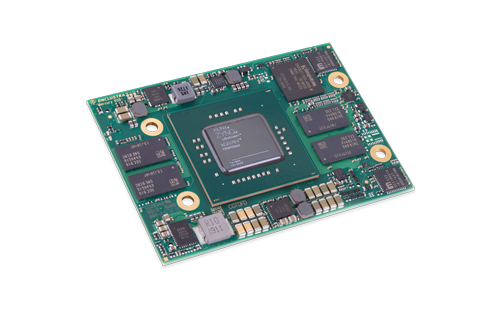

产品型号仙女座XZU65核心板

n 基于Xilinx's Zynq Ultrascale+™ MPSoC 7EV/11EG

n PS端(DDR4 ECC SDRAM)和PL端(DDR4 SDRAM)2个独立的内存通道

n 32.4 GByte/sec内存带宽

n 提供PCIe® Gen3 x 16,PCIe Gen2 x 4,USB 3.0,2 x Gigabit Ethernet

n 提供工业级型号

n 采用ADM6-60 Samtec连接器,引出322个用户I/O

n 提供Linux BSP和工具链

n 功能强大、身材小巧的核心板

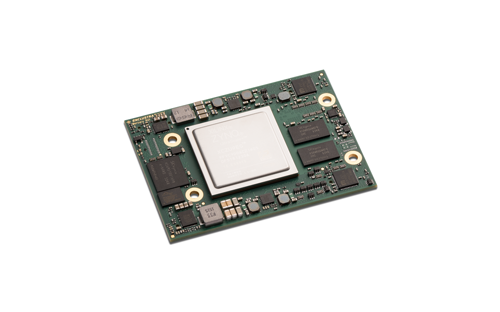

仙女座XZU90核心板

n 基于Xilinx's Zynq Ultrascale+™ MPSoC XCZU17EG/19EG 1760封装

n 具备ECC(Error Correction Code,纠错码)的DDR4 SDRAM,最高8 GB

n 19.2 GByte/sec内存带宽

n 提供最多5 x PCIe® Gen3 x16, PCIe Gen2 x4, USB 3.0 和 2 x Gigabit Ethernet

n 多个型号可供选择,提供工业级型号

n 采用6个ADM6-60 Samtec连接器,引出686个用户I/O

n 提供Linux BSP和工具链

n 功能强大、身材紧凑的FPGA核心板

水星Mercury XU5核心板

n 基于Xilinx's Zynq Ultrascale+™ MPSoC XCZU2CG/4CG/2EG/3EG/4EV/5EV

n PS端(DDR4 ECC SDRAM)和PL端(DDR4 SDRAM)2个独立的内存通道

n 最高24 GByte/sec内存带宽

n 提供PCIe® Gen3 x 4,PCIe Gen2 x 4,2 x USB 3.0,2x Gigabit Ethernet

n 多个型号可供选择,提供工业级型号

n 采用2个168-pin Hirose FX10连接器,引出178个用户I/O

n 提供Linux BSP和工具链

n 功能强大、身材小巧的FPGA核心板

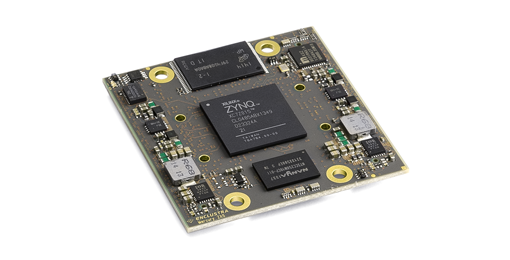

火星Mars XU3核心板

n 基于Xilinx's Zynq Ultrascale+™ MPSoC XCZU2CG/2EG/3EG

n 将CPU系统的灵活性与并行处理能力和FPGA系统的实时能力相结合

n 高速DDR4 SDRAM

n 支持模拟差分输入

n 多个型号可供选择,提供工业级型号

n 支持USB 3.0,CAN,千兆以太网和PCIe® Gen2 x4

n 提供Linux BSP和工具链

水星Mercury+ XU1核心板

n 基于Xilinx's Zynq Ultrascale+™ MPSoC XCZU6CG/6EG/9EG/15EG

n 具备ECC(Error Correction Code,纠错码)的DDR4 SDRAM

n 19.2 GByte/sec内存带宽

n 提供PCIe® Gen2 x 4,2 x USB 3.0,2 x Gigabit Ethernet

n 多个型号可供选择,提供工业级型号

n 采用3个168-pin Hirose FX10连接器,引出294个用户I/O

n 提供Linux BSP和工具链

n 功能强大、身材小巧的FPGA核心板

水星Mercury+ XU6核心板

n 基于Xilinx's Zynq Ultrascale+™ MPSoC XCZU2CG/4CG/2EG/3EG/4EV/5EV

n 具备ECC(Error Correction Code,纠错码)的DDR4 SDRAM

n 最高19.2 GByte/sec内存带宽

n 提供PCIe® Gen3 x 4, PCIe Gen2 x 4,2 x USB 3.0,Gigabit Ethernet

n 多个型号可供选择,提供工业级型号

n 采用3个168-pin Hirose FX10连接器,引出294个用户I/O

n 提供Linux BSP和工具链

n 功能强大、身材小巧的FPGA核心板

水星Mercury+ XU7核心板

n 基于Xilinx's Zynq Ultrascale+™ MPSoC XCZU6EG/9EG/15EG

n PS端(DDR4 ECC SDRAM)和PL端(DDR4 SDRAM)2个独立的内存通道

n 最高28.8 GByte/sec内存带宽

n 提供PCIe Gen2 x 4,2 x USB 3.0,2x Gigabit Ethernet

n 多个型号可供选择,提供工业级型号

n 采用3个168-pin Hirose FX10连接器,引出236个用户I/O

n 提供Linux BSP和工具链

n 功能强大、身材小巧的FPGA核心板

水星Mercury+ XU8核心板

n 基于Xilinx's Zynq Ultrascale+™ MPSoC XCZU4CG/5EV/7EV

n PS端(DDR4 ECC SDRAM)和PL端(DDR4 SDRAM)2个独立的内存通道

n 最高28.8 GByte/sec内存带宽

n 提供PCIe® Gen3 x 16,PCIe Gen2 x 4,2 x USB 3.0,2x Gigabit Ethernet

n 多个型号可供选择,提供工业级型号

n 采用3个168-pin Hirose FX10连接器,引出236个用户I/O

n 提供Linux BSP和工具链

n 功能强大、身材小巧的FPGA核心板

水星Mercury+ XU9核心板

n 基于Xilinx's Zynq Ultrascale+™ MPSoC XCZU4CG/5EV/7EV

n PS端(DDR4 ECC SDRAM)和PL端(DDR4 SDRAM)2个独立的内存通道

n 最高38.4 GByte/sec内存带宽

n 提供PCIe® Gen3 x 16,PCIe Gen2 x 4,2 x USB 3.0,2x Gigabit Ethernet

n 多个型号可供选择,提供工业级型号

n 采用3个168-pin Hirose FX10连接器,引出192个用户I/O

n 提供Linux BSP和工具链

n 功能强大、身材小巧的FPGA核心板

仙女座Pluto XZU20核心板(早期试用阶段)

- 基于全可编程 AMD Zynq™ UltraScale+™ MPSoC 架构

- 低延迟 FPGA 可编程逻辑,实现系统实时响应

- 低功耗 LPDDR4(PS 端)

- 4.26 GB/s 内存带宽

- 多种低功耗模式,低功耗状态下功耗低至 0.1 瓦

- 提供 USB 3.0 和千兆以太网接口

- 支持工业级温度范围

- 596 球 LGA 焊盘,多达 106 个用户 I/O

- 提供 Linux BSP 和工具链

- 强劲紧凑的 FPGA 板卡

Xilinx Zynq 7000

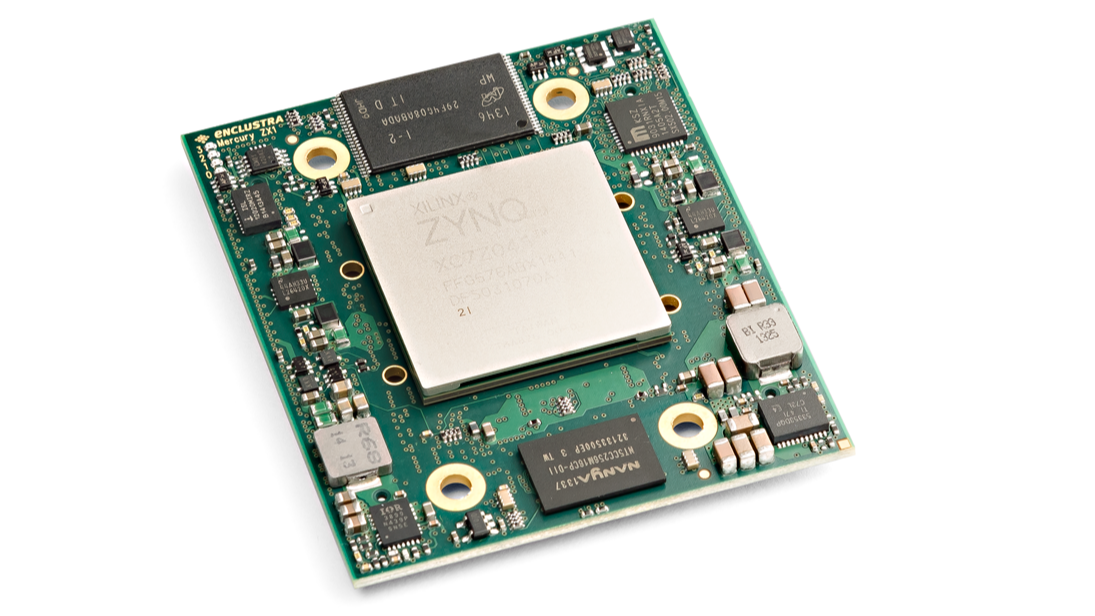

产品型号水星Mercury ZX1核心板

n 基于Xilinx's Zynq-7000完全可编程SoC

n 将CPU系统的灵活性与FPGA系统的并行处理能力和实时能力相结合

n 提供PCIe® Gen2 x 8,USB 2.0,Gigabit Ethernet

n 双百兆以太网,可用于工业以太网,如PROFINET、EtherCAT、POWERLINK、Ethernet/IP

n 工业级

n 采用2个168-pin Hirose FX10连接器,封装小

n 提供Linux BSP和工具链

n 功能强大、身材小巧的FPGA核心板

水星Mercury ZX5核心板

n 基于Xilinx's Zynq-7000完全可编程SoC

n 将CPU系统的灵活性与FPGA系统的并行处理能力和实时能力相结合

n 支持模拟差分输入

n 工业级

n USB 2.0,CAN,Gigabit Ethernet

n 提供Linux BSP和工具链

n 功能强大、身材小巧的FPGA核心板

火星Mars ZX3核心板

n 基于Xilinx's Zynq-7020完全可编程SoC

n 将CPU系统的灵活性与FPGA系统的并行处理能力和实时能力相结合

n 支持模拟差分输入

n 工业级

n USB 2.0,CAN,Gigabit Ethernet

n 提供Linux BSP和工具链

n 功能强大、身材小巧的FPGA核心板

火星Mars ZX2核心板

n 基于Xilinx's Zynq-7010/20完全可编程SoC

n 将CPU系统的灵活性与FPGA系统的并行处理能力和实时能力相结合

n 支持模拟差分输入

n 工业级

n USB 2.0,CAN,Gigabit Ethernet

n 提供Linux BSP和工具链

n 功能强大、身材小巧的FPGA核心板

Xilinx Kintex-7

水星Mercury KX1核心板

n 高性价比的Xilinx Kintex-7 28nm FPGA

n 基于Cypress EZ-USB®FX3™,提供一个强大且易于使用的USB 3.0设备接口

n 提供2 × Gigabit Ethernet,可用于高带宽/低延时网络

n 提供PCIe Gen2 x4 接口,可用于高速数据传输

n 提供工业级型号

n 尺寸比信用卡还要小

n 功能强大、身材小巧的FPGA核心板

水星Mercury+ KX2核心板

n 高性价比的Xilinx Kintex-7 28nm FPGA

n 提供2 × Gigabit Ethernet,可用于高带宽/低延时网络

n 提供PCIe Gen2 x8终端,可用于高速数据传输

n 高达12.8 GByte/sec内存带宽

n 提供工业级型号

n 尺寸比信用卡还要小

n 功能强大、身材小巧的FPGA核心板

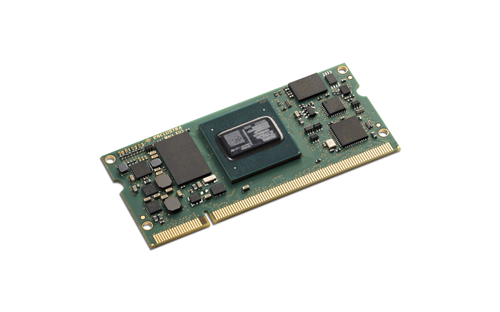

Xilinx Artix-7

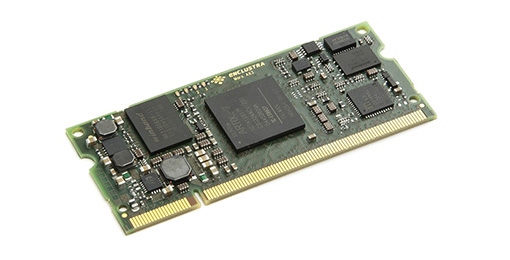

产品型号火星 AX3核心板

n 低成本、低功耗的FPGA

n 35k-100k逻辑单元,40k-120k触发器和90- 240 DSP slices

n 采用标准的、紧凑的、被广泛支持的SO-DIMM连接器

n 支持千兆以太网和模拟输入

n 工业级

n 强大而紧凑的FPGA核心板

Xilinx Spartan-6

火星 MX1核心板

n 低成本、低功耗的FPGA

n 采用标准的、紧凑的、被广泛支持的SO-DIMM连接器

n 工业级

n 适用于工业总线(如PROFINET、EtherCAT、POWERLINK或Ethernet/IP)的双百兆以太网

n 强大而紧凑的FPGA核心板

火星 MX2核心板

n 低成本、低功耗的FPGA

n 双数千兆位串行接口传输器

n 采用标准的、紧凑的、被广泛支持的SO-DIMM连接器

n 工业级

n 提供PCIe,Gigabit Ethernet

n 强大而紧凑的FPGA核心板

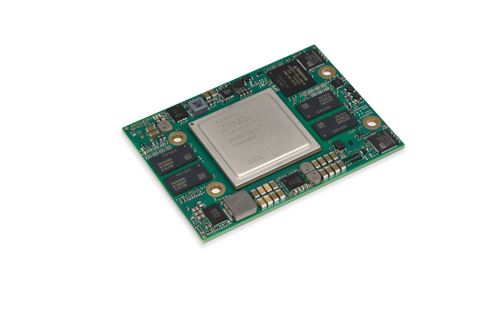

Intel (Altera) Arria 10

水星Mercury+ AA1核心板

n Intel Arria® 10 基于ARM处理器的SoC FPGA

n 提供USB 3.0, PCIe® Gen3 x8和Gigabit Ethernet

n 具备ECC(Error Correction Code,纠错码)的DDR4 SDRAM

n 9.6 GByte/sec内存带宽

n 提供工业级型号

n 尺寸比信用卡还要小

n 提供Linux BSP和工具链

n 功能强大、身材小巧的FPGA核心板

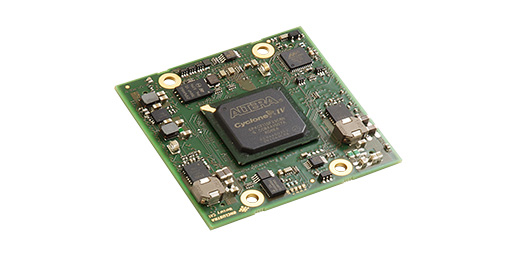

Intel (Altera) Cyclone IV / V

产品型号水星Mercury SA1核心板

n Intel Cyclone® V基于ARM处理器的SoC FPGA

n 提供USB 2.0,PCIe® Gen1 ×4和Gigabit Ethernet

n 工业级

n 尺寸比信用卡还要小

n 提供Linux BSP和工具链

n 功能强大、身材小巧的FPGA核心板

水星Mercury+ SA2核心板

n Intel Cyclone® V基于ARM处理器的SoC FPGA

n 提供USB 3.0,USB 2.0,PCIe® Gen1/Gen2 ×4,Gigabit Ethernet,2 × 10/100Mbs Ethernet

n 工业级

n 尺寸比信用卡还要小

n 提供Linux BSP和工具链

n 功能强大、身材小巧的FPGA核心板

水星Mercury CA1核心板

n Intel Cyclone IV E FPGA

n FTDI USB 2.0

n Gigabit Ethernet

n 提供工业级型号

n 尺寸比信用卡还要小

n 功能强大、身材小巧的FPGA核心板

火星MA3核心板

n Intel Cyclone® V SoC

n 结合了CPU系统的灵活性和FPGA原始的、实时的并行处理能力

n 提供USB 2.0,CAN和Gigabit Ethernet

n 工业级

n 提供Linux BSP和工具链

n 功能强大、身材小巧的FPGA核心板

Microchip Polarfire

水星Mercury+ MP1核心板

n 基于Microchip的PolarFire SoC打造

n MSS(DDR4 ECC SDRAM)和FPGA(DDR4 SDRAM)2个独立的内存通道

n 具备ECC(Error Correction Code,纠错码)的DDR4 SDRAM

n 最高19.2 GByte/sec内存带宽

n 提供最多PCIe® Gen2 x4,USB 2.0和2 x Gigabit Ethernet接口

n 提供工业级型号

n 3个168-pin Hirose FX10连接器提供295个用户I/O

n 提供Linux BSP和工具链

n 功能强大、身材小巧的FPGA核心板

-

底板/开发板

水星Mercury(+)

产品型号水星Mercury+ ST1底板/开发板

n 兼容所有水星Mercury(+)系列FPGA和SoC核心板

n 适用于从原型到量产

n 身材紧凑(120 × 100 mm)

n 为视频应用而设计的大量接口

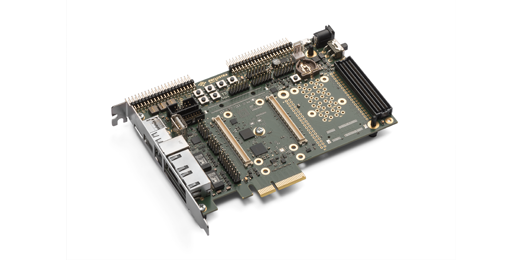

水星Mercury+ PE1底板/开发板

n 兼容所有水星Mercury(+)系列FPGA和SoC核心板

n PCIe® Gen2 x 4,USB 3.0,多个USB2.0接口

n 丰富的I/O适用于几乎所有应用

n 适用于从原型到量产

n 标准PEIe尺寸(PCB 160 × 111.2 mm)

n 可单独作为开发板使用(而非PCIe卡)

水星Mercury+ PE3底板/开发板

n 兼容所有水星Mercury(+)系列FPGA和SoC核心板

n 提供PCIe® ×8, 支持DP的USB Type-C 3.0连接器,USB 3.0 host连接器

n QSFP+/SFP+接口,用于高速通信应用

n 适用于从原型到量产

n 171 × 112.4 mm,含PCIe ×8边缘连接器

n 可单独作为开发板使用(而非PCIe卡)

火星Mars

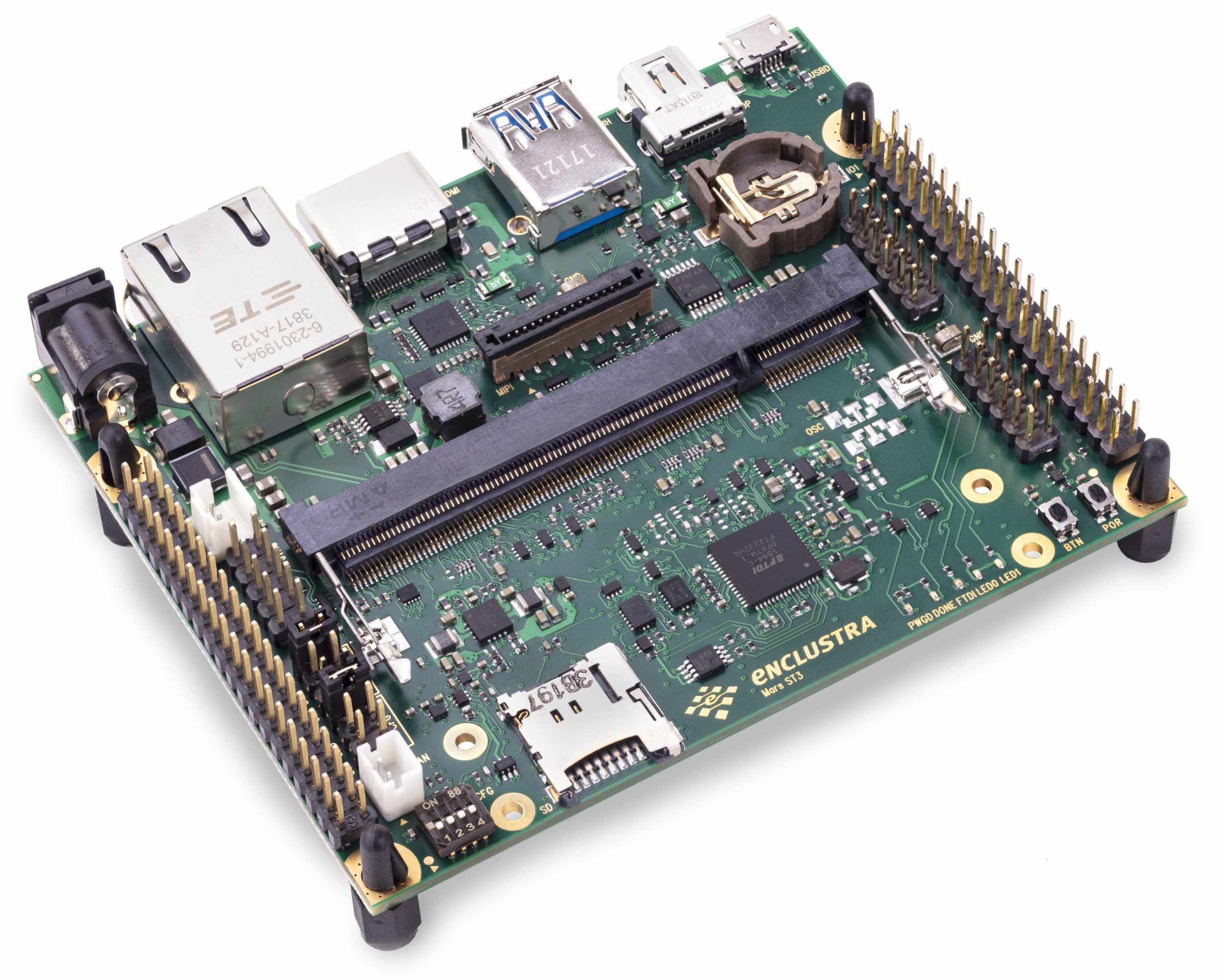

火星Mars ST3底板/开发板

n 与所有火星Mars系列FPGA和SoC核心板兼容

n 为视频应用而设计的大量接口

n 身材紧凑(100 × 80 mm)

n 适用于从原型到量产

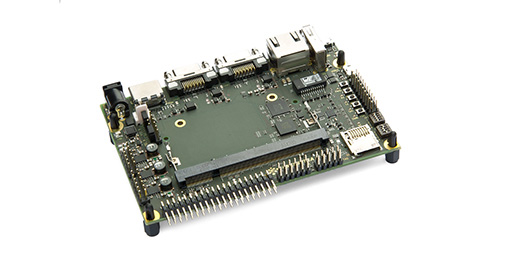

火星Mars EB1底板/开发板

n 与所有火星Mars系列FPGA和SoC核心板兼容

n 适用于几乎所有应用的I/O接口

n 适用于从原型到量产

n 身材紧凑(p-ITX, 100 × 72 mm)

n DC或者USB供电

火星Mars PM3底板/开发板

n 与所有火星Mars系列FPGA和SoC核心板兼容(XU3除外)

n USB 3.0的数据传输速率超过300MB/s

n 适用于从原型到量产

n 身材紧凑(p-ITX, 100 × 72 mm)

Xilinx ZU+ MPSoC开发套件

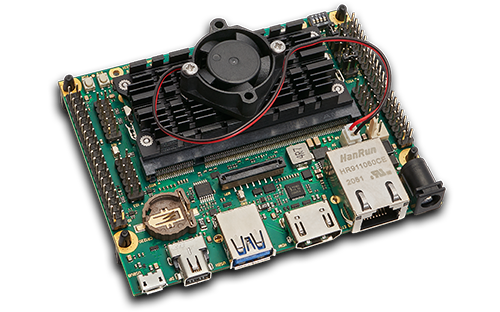

XU3-2CG/3EG开发套件

为了尽可能地缩短用户的产品上市时间,瑞苏盈科为其产品提供了广泛的设计支持和一个全面的生态系统,提供所有所需的硬件、软件和支持材料。详细的文档和参考设计使上手变得容易:提供了用户手册、用户原理图、3D模型、PCB封装、差分I/O净长度表和基于linux的板级支持包(BSP)。 结合现成的底板和散热器,开发FPGA项目从未如此容易。

开发套件包含2个例程:AI人脸检测和图像分类,例程基于ResNet50和Xilinx Vitis AI,瑞苏盈科提供了现成的二进制文件和源代码、如何自己构建它的大量文档。

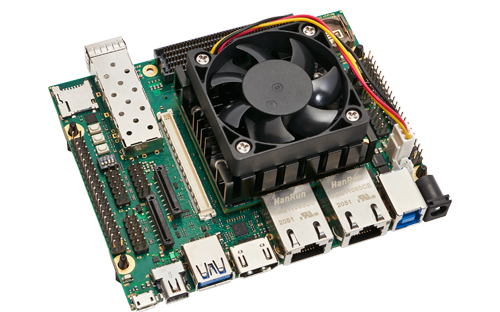

XU5-4EV/5EV开发套件

为了尽可能地缩短用户的产品上市时间,瑞苏盈科为其产品提供了广泛的设计支持和一个全面的生态系统,提供所有所需的硬件、软件和支持材料。详细的文档和参考设计使上手变得容易:提供了用户手册、用户原理图、3D模型、PCB封装、差分I/O净长度表和基于linux的板级支持包(BSP)。 结合现成的底板和散热器,开发FPGA项目从未如此容易。

开发套件包含2个例程:AI人脸检测和图像分类,例程基于ResNet50和Xilinx Vitis AI,瑞苏盈科提供了现成的二进制文件和源代码、如何自己构建它的大量文档。

仙女座Andromeda

仙女座Andromeda底板/开发板

兼容所有 Andromeda SoC 模块(RFSoC 模块除外)

提供 PCIe x8 及 2 个 USB Type-C 3.0 接口

配备 QSFP28/SFP28 接口,适用于高速通信应用

支持从原型开发到批量生产的全流程应用

尺寸 170 × 111.15 mm,带 PCIe x8 边缘连接器

亦可作为独立板卡使用(非 PCIe 扩展卡模式)

- 展会&活动

- 成功案例&Demo

- 关于我们